Supported Devices: K7, V7. UltraScale. UltraScale+

Encrypted Netlist: NO

IP Format: Encrypted Netlist

Product Description

Developed based on AMD/Xilinx 10G Ethernet MAC IP, MTU supports up to 9000 bytes of data transmission, standard AXI4 Stream interface, supports AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7, Kintex 7, Zynq 7030/7035/7045/7100 Series FPGA devices. The 10G Ethernet with high bandwidth and low latency ensures fast data transmission and real-time processing, while the UDP protocol stack further improves the efficiency and accuracy of data transmission.

We provide you with a fast, reliable, low-cost, and high-performance solution that significantly shortens the time to market and is suitable for high bandwidth, low latency, and high-speed data transmission scenarios.

Applications

● Data Center

● Cloud Computing Storage

● AI

● Machine Learning

● Telecommunications

● Industrial Automation

● Internet of Things

● Medical

● Gene Sequencing

● 4K/8K HD Video Transmission

● Scientific Research Experiment

● Financial Transactions

● Test Measurement

Key Features

● Implement an ARP/IPV4/ICMP/UDP protocol stack that complies with the IEEE802.3 standard based on the OSI layered model.

● Supports ARP for obtaining or sending MAC addresses.

● Supports ICMP for responding to Ping commands.

● ARP responds to all incoming requests, only stores 10 ARP tables.

● No UDP packets are sent if the ARP table is not established.

● 10Gbps Ethernet connection, supporting UDP/IP checksum processing, calculating CRC by the MAC IP.

● Developed based on AMD/Xilinx 10G MAC IP, supporting MTU up to 9000 Bytes and a minimum 64 Bytes data transmission size.

● AXI4 Stream interface for users, with the protocol stack using a clock of 156.25 MHz generated by the MAC IP, and a 10 Gbps data bus width of 64 bits.

| Ceres::Template.singleItemTechnicalDataAttribute | Ceres::Template.singleItemTechnicalDataValue |

|---|---|

| Identificación de artículo | 102756 |

| Estado | |

| Modelo | AXC-UDP-10G-R1.0 - One-time |

| Fabricante | Alinx Electronic Limited |

| País de origen | |

| Contenido | 1 undefined |

| Peso | 1000 g |

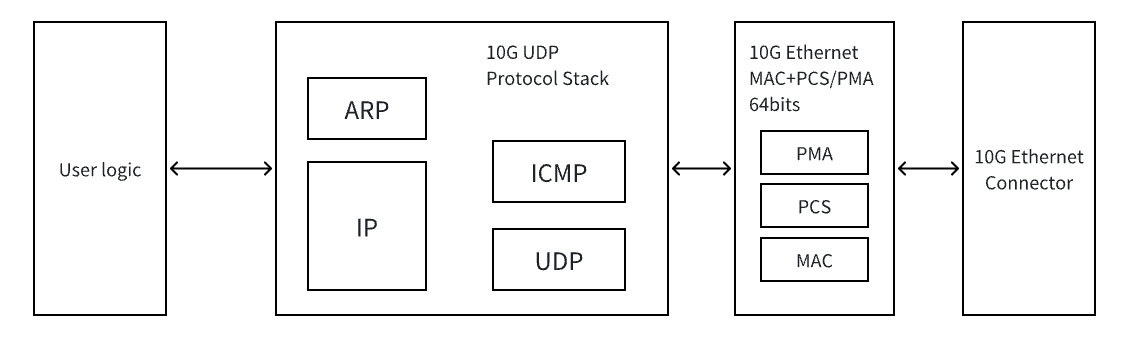

Example of Application Structure Diagram

The diagram below shows the position of the 10G Ethernet UDP/IP Protocol Stack FPGA IP Core within the system design:

The 10G Ethernet UDP/IP Protocol Stack FPGA IP Core uses standard AXI4-Stream interfaces for both the user interface and the Ethernet MAC + PCS/PMA IP interface. The Ethernet MAC + PCS/PMA can be any third-party IP. In the provided design example, AMD/Xilinx 10G/25G Ethernet Subsystem IP is used.

IP Resource Utilization Table

The evaluation of IP resource consumption adopts AMD Zynq Ultrascale+ MPSoC series FPGA Development Kits/boards, which provides a fully functional design platform for building communication centric Ethernet applications. The AMD Zynq Ultrascale+ MPSoC series FPGA development boards/Kits provides an out of the box hardware platform with reference designs, which can shorten development time and allow you to focus on your target applications.

Note: Actual IP resource consumption is affected by the consumption of other logical resources during instantiation.

Product Matrix

IP Information

Documentation

10G UDP/IP protocol stack IP Core User Guide

IP Provided Format

Encrypted Netlist

Design Language

Verilog

Development Tool

Vivado 2020.1

Supported Devices

AMD/Xilinx Zynq UltraScale+ RFSoC, Zynq UltraScale+ MPSoC, Virtex UltraScale+, Kintex UltraScale+, Artix UltraScale+, Virtex UltraScale, Kintex UltraScale, Virtex 7, Kintex 7, Zynq 7030/7035/7045/7100

There are two licensing methods available for our IP cores

Licensing Types:

One-Time License: Unlimited usage for a specific Xilinx FPGA series (e.g. 7 Series, UltraScal. UltraScale+). Not tied to a specific PC, No MOQ.

DNA Activation Code: Tied to each FPGA chip's unique DNA: licensed per unit. Suitable for low-volume customers, MOQ applies.

Security & Traceability:

Each IP core includes a customer-specific internal code distribution or leakage.

Alinx Electronic Limited

Alinx 10G Ethernet UDP/IP Stack FPGA IP Core for Network Acceleration

Developed based on AMD/Xilinx 10G Ethernet MAC IP, MTU data transmission up to 9000 bytes, AXI4 stream interface, supporting Kintex 7 / Virtex 7 / UltraScale / Ultrade+ / Zynq UltraScale+ Series FPGA devices, high bandwidth and low latency, fast data transmission and real-time processing, accurate and efficient data transmission of UDP protocol stack. Please contact b2b (at) mirifica.eu for the alternative DNA Activation unit price version.

Código de artículo VAR-827004344

Número de pieza del fabricante: AXC-UDP-10G-R1.0 - One-time

Código aduanero:

El producto se envía desde Riedlingen, Alemania.

Los clientes suelen ver

También te puede interesar